Systemverilog Macros With Arguments

SystemVerilog macros might sound intimidating, but trust me, they're like secret shortcuts in your coding toolbox! They're especially fun when you add arguments, because that's when they really start to shine. Think of them as mini-programs that write code for you, saving you time and reducing errors. Who wouldn't want that?

Why should you care? Well, if you're a beginner, macros with arguments can help you understand code reuse and write more efficient designs from the get-go. You can avoid repetitive typing and focus on the bigger picture. For hobbyists tinkering with FPGA projects, macros can streamline complex tasks like configuring memory interfaces or generating test patterns. Imagine setting up intricate register maps with just a few lines of code! Even for families (yes, really!), if you're introducing kids to programming logic, simplified macros can be a great way to demonstrate abstraction and code organization without diving into deep syntax right away. It makes coding feel less daunting.

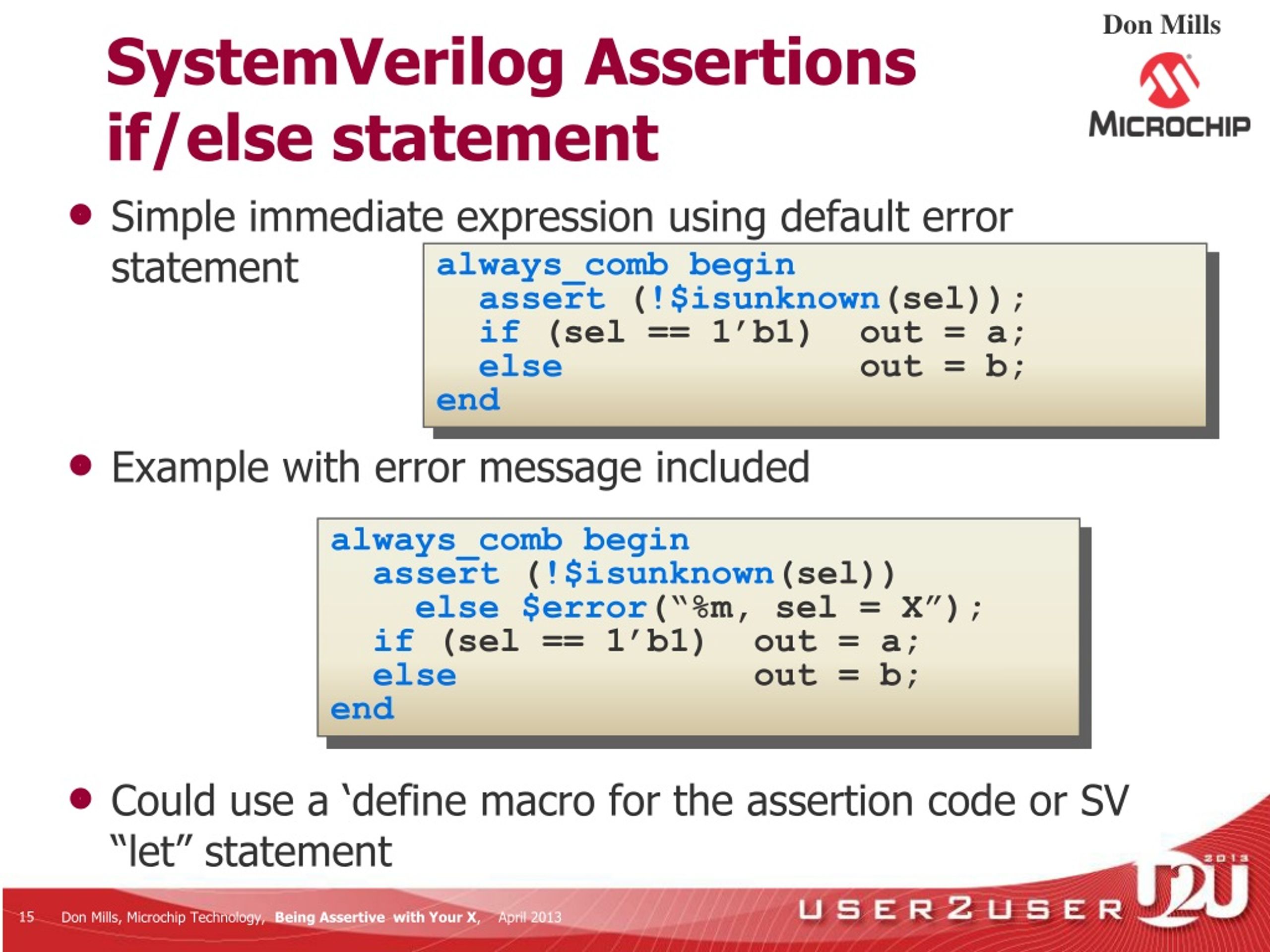

So, what are these magic arguments? Let's say you frequently need to print the value of a variable with a specific format. Instead of writing the same ` $display` statement over and over, you can define a macro like this:

Must Read

`define PRINT_VALUE(VAR, FORMAT) $display("Value of " #VAR " is " FORMAT, VAR);

Now, whenever you want to print a value, you can simply call the macro:

`PRINT_VALUE(my_signal, %h); // Prints the hexadecimal value of my_signal

`PRINT_VALUE(counter, %d); // Prints the decimal value of counter

See how we passed `my_signal` and `counter` as arguments, and the macro substituted them into the `$display` statement? The `#` operator turns the argument into a string, so you can include the variable's name in the output. The `FORMAT` argument allows you to customize the printing format.

Here's another example, this time for generating register definitions:

`define DEFINE_REGISTER(REG_NAME, ADDR, WIDTH) \

logic [WIDTH-1:0] REG_NAME; \

parameter integer ADDR = 'hADDR;

And you'd use it like this:

`DEFINE_REGISTER(control_reg, 0x10, 8); // Defines an 8-bit register named control_reg at address 0x10

Practical tips for getting started:

- Start small: Begin with simple macros that solve common, repetitive tasks.

- Use descriptive names: Make your macro names clear and understandable.

- Document your macros: Add comments explaining what each macro does and how to use it.

- Test thoroughly: Always verify that your macros are working as expected.

- Embrace the backslash: Use the backslash (

\) to continue macro definitions onto multiple lines for better readability.

Macros with arguments can significantly improve your SystemVerilog coding experience. They reduce redundancy, enhance code readability, and make your designs more maintainable. So, give them a try and discover the power and fun of writing code that writes code!